The ESP32 effort has been a long road with twists and significant turns, but is now on track to be a significantly better energy monitor than anything originally imagined. It started out as just a port of the ESP8266 sampling method using the extra processor to essentially increase the channel sampling rate by 50%. Can you believe that was 3 years ago?

Covid had a lot to do with the delays. Then, as I started back in, I quickly realized that the ESP32-VROOM-32 was old school. Enter the ESP32-S3. It has a lot more resources. As I pondered porting the old effort to the S3, I took another look at sigma-delta ADCs. Once I realized that they were much faster and more accurate than the MCP3208 SAR ADCs, I started to work up a design. A lot of the older architecture was basically useful. These ADCs can handle up to 8 inputs simultaneously and stage the results for SPI retrieval in one transaction. Moreover, they run continuously sampling every AC cycle on all channels and produce 24 bit results - 4,096 times the resolution of the MCP3208.

The Texas Instruments chip family also had a new variant that is certified for isolation from line voltages. This was key to eliminating the AC reference transformer(s) and their associated phase-delay. It took awhile to get my hands on some, initially I had to buy TI evaluation boards and adapt them to the ESP32. Now they are more available.

Due to the continuous sampling on all channels, the challenge was to rip the data from a voltage reading ADC and then up to four 8 channel current sensing ADCs - all in 125us then be ready to do it again. Steady state its fairly easy but there are several factors that affect timing and the worst case scenarios needeed to be identified and planned for.

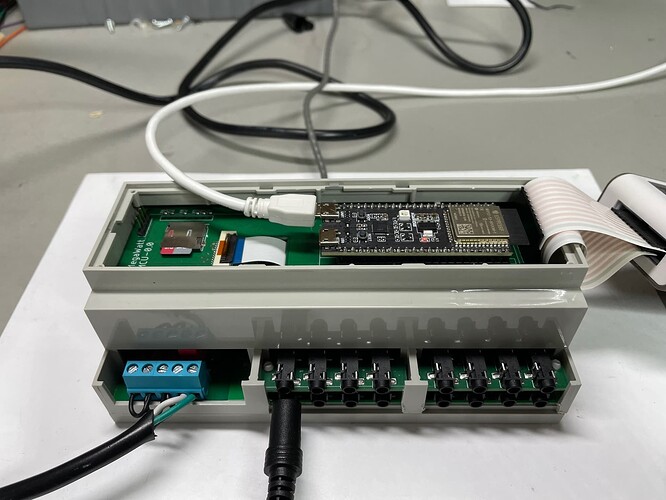

This could be a longer story, but I’ll stop there and simply say that I think all of the real difficult technical challenges seem to be resolved. After several iterations of hardware, I’ve got a 32 input unit that fits into a hacked up DIN enclosure.

On the left is the AC input. Left to Right L3-L2-L1-Neutral-Earth. Sixteen inputs are visible, there are 16 more on the other side. The USB and ribbon cables are for serial diagnostics and logic analyser to monitor stability and performance. So far it seems to be rock solid.

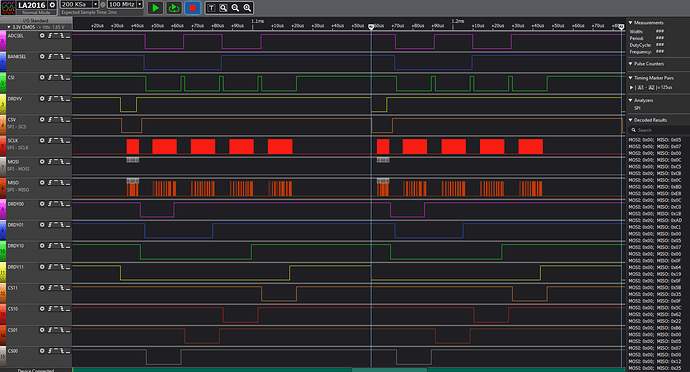

Here is the “EKG” from the logic analyser:

It’s pretty busy. Two 125us frames are visible. The frame on the right has vertical lines bounding it. It begins with the Voltage ADC coming ready with new samples. The ESP32 senses that with DRDYV, sets lowers chip select CSV and reads the values of the three voltage inputs L1, L2 and L3 evident by the activity on the SPI SCLK, MOSI and MISO.

The current ADCs are organized into two banks, 0 and 1. Each bank has two ADCs, 0 and 1. So an ADC is addressed by it;s bank and adc 00 01 10 and 11. As the ADCs complete conversions, they signal ready on DRDY00, DRDY01 etc. These signals are multiplexed into a single DRDY signal using BANKSEL and ADCSEL. So the ESP32 sampler checks each ADC in turn. When a ready ADC is found, an encoder chip is used to route the chip select CSI to the appropriate CS00, CS01 etc. and the ADC data is read.

As each of the ADCs is read, the data from the last sample is preprocessed to a set of accumulators. This is done, for the most part, asynchronously as the SPI transfer is happening.

Every second, at a zero crossing, the sampler switches to a new accumulator and signals the Post Process task running on the other core to process the data into the datalog.

There are a lot of subtleties involved. For instance, the ADCs can advance or delay the sampling of each individual channel by a specified time. Without getting into the nuances of that, suffice to say it’s non-trivial, but also that setting and handling the delay is dynamic so that like the old IoTaWatt V5, it can configure new or changed CTs on the fly without interruption.

This represents a significant milestone, and with the hardware solid I can get down to my list of essential firmware improvements. While this stock enclosure does the trick to package the prototype, I still need to design an appropriate enclosure and at a minimum get it 3D printed. Along with that will be an effort to eliminate the ESP32-DEVKITC in favor of discrete components.

Not sure if or when this will become a commercial product, but I think the viability is becoming more certain.